# Low – Power Low–Voltage Asynchronous Delta–Sigma Modulator

Bharath Ch<sup>1</sup>, Sailaja M<sup>2</sup>

<sup>1</sup>Student, VLSI & Embedded Systems, Department of Electronics and Communication Engineering, Jawaharlal Nehru Technological University, Kakinada, Andhra Pradesh, India.

<sup>2</sup>Professor, Department of Electronics and Communication Engineering, Jawaharlal Nehru Technological University, Kakinada, Andhra Pradesh, India.

$Corresponding \ Author: \ bharathchitikada@gmail.com$

**Abstract:** - Due to the increase in the ultralow - power VLSI systems this work is one of the solution for the ultralow - voltage bulk driven (BD) asynchronous delta – sigma modulator which is implemented in 54nm CMOS technology with  $V_{DD}$  supply as 300 mV, the circuit leads to the total power consumption of 15.35 pW. The above mentioned result have been achieved employing a highly linear transconductor (Gm – C) as an integrator it is as similar as an R – C integrator, asynchronous delta – sigma modulator (ADSM) and a hysteretic comparator based on non - tailed BD differential pair with un buffered op-amps since it has very high output resistance than buffered op-amp. The main objective of this paper is to offer good accuracy even at low supply voltages with good frequency response.

Key Words — Bulk driven asynchronous delta-sigma modulator, Linear transconductance integrator, Hysteric Comparator, Buffered opamps, Unbuffered op-amps, Ultralow-power VLSI systems.

### I. INTRODUCTION

With the significant increase in the ultralow - power and ultralow - voltage VLSI systems, the supply voltages are made as low as 0.25 - 0.3 volts. In order to meet the requirements posed by such sources, a number of innovative circuit solutions have recently been developed, one of such sources is reviewed in this paper. In order to meet the requirements, the solutions mostly including unbuffered opamps, linear transconductors and delta - sigma modulators (DSMs) are used with the concept of bulk driven transistors. The most interesting solutions include unbuffered op-amps [1], [2], linear transconductors [3], [4], and delta-sigma modulators (DSMs) [5]- [7]. Among different architectures, the asynchronous delta - sigma modulators (ADSM) have gained most advantages in recent years. One of the greatest challenges for analog designers dealing with sub-0.5-V circuits is the realization of power efficient and precise analog-to-digital converters (ADCs). ADSMs translates band-limited analog input signal to an asynchronous modulated square wave which doesn't require clocking and offers good accuracy at even low supply voltages. Owing to its principle of operation, the circuit has a simple structure, does not require any clocking, is free of quantization noise, has good frequency response, and offers good accuracy at very low supply voltages [8]–[10]. It is also worth to point out that ADSM architecture is well sufficiently compatible with contemporary CMOS technologies. An interesting approach to the design of an ULV ADSM based on BD building blocks and exploiting a single-ended RC integrator has recently been proposed in [6]. The circuit offers reasonable performance in an ULV environment, nevertheless, it was realized using low VTH CMOS process and required several off-chip passive

elements. The proposed circuit offers similar performance as the one described in [6] but can operate with much lower relative supply voltage (VDD/VTH). The fully differential architecture of this circuit allows reducing the even harmonics of the output signal, thus improving the linearity and consequently the resolution of ADSM. In addition, since the RC integrator in [6] has been replaced with a Gm-C integrator in the proposed design, the above-mentioned external RC elements applied in [6] are avoided, which is another advantage of the proposed solution. The design experimentally confirms proper operation of the transconductor [4] and the common-mode feedback (CMFB) circuit [12], which in original papers was validated only by simulations. In addition, a new ULV BD comparator has been designed and investigated. All the blocks were designed and optimized for application in ULV ADSM and the design tradeoffs for such application have been discussed. The design experimentally confirms the feasibility of the proposed circuits and investigates their performance in ULV ADSM.

#### II. ASYNCHRONOUS DELTA-SIGMA MODULATOR

Below is the block diagram of 1<sup>st</sup> order ADSM consists of linear trans-conductance integrator, DAC and comparator. The ADSM generates a square-wave output signal with both, the duty cycle 'd', and the oscillation period 'To' being functions of the input amplitude, according to the following formulas [8]:

$$d = \frac{1+u}{2} \tag{1}$$

$$T_0 = \frac{1}{f_0(1 - u^2)} \tag{2}$$

International Journal of Progressive Research in Science and Engineering Volume-1, Issue-8, November-2020

www.ijprse.com

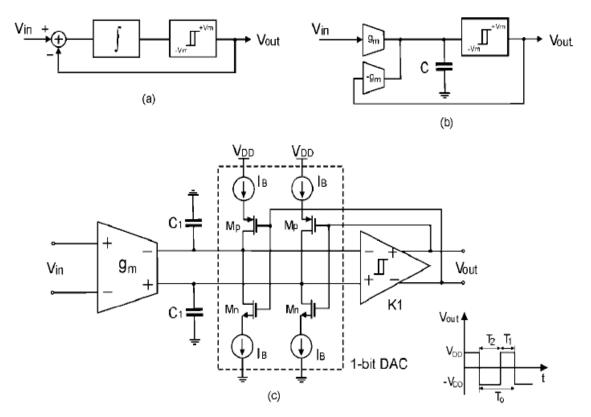

Fig. 1. (a) First-order ADSM. (b) Realization with linear transconductors. (c) Proposed fully differential ADSM.

Where, u = Vin/Vm is the normalized input amplitude, with the normalization voltage Vm equal to the output voltage level, and fo is the constant center frequency. The block diagram of the proposed fully differential ADSM is shown in Fig. 1(c). The circuit consists of a continuous time Gm–C integrator, a hysteretic comparator (K1), and a 1-bit digitalto-analog converter (1-bit DAC) in the form of the switched current sources IB, with transistors Mp and Mn operating as switches. Note that in the proposed realization, the feedback signal depends on the value of IB rather than the output voltage level as in Fig. 1(a), which makes the proposed circuit less sensitive to power supply variations. The duty cycle for the considered circuit is given as

$$d = \frac{T_1}{T_1 + T_2} = \frac{1+u}{2} \tag{3}$$

while the total time period of the output square wave to is given as

$$T_0 = T_1 + T_2$$

The normalized input signal u can also be expressed in

terms of *T*<sub>1</sub> and *T*<sub>2</sub> as

$$u = \frac{T_1 - T_2}{T_1 + T_2}$$

Hence, the input signal could easily be recovered by the measurement of the periods  $T_1$  and  $T_2$ . This could be done with a reconstruction digital circuit [8].

# III. TRANSISTOR LEVEL REALIZATION

# A. $G_m - C$ Integrator

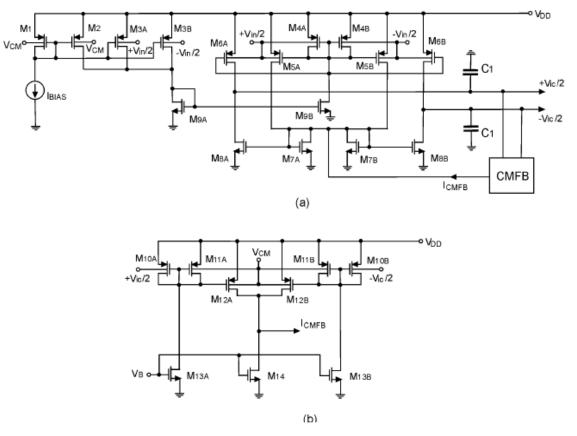

In this design, this integrator approach has been used to design a voltage integrator. This integrator provides better power efficiency and larger input resistance than their RC counterparts and allow avoiding large resistors which are difficult to integrate. The Gm–C integrator employed in the considered design [Fig. 2(a)] consists of the BD linear transconductor proposed in [4] and the CMFB circuit in [6]. The Gm stage is characterized by excellent linearity of its transfer characteristic, even for VDD as low as 0.25 V to 0.3 V.

For all the p – channel transistors, the common mode voltage  $V_{CM}$  is made equal to zero. Parameters for the integrator are given as follows for the operation of the circuit

in Table I. The supply voltage for the circuit is between 0.25 volts.

Fig. 2. (a) BD Gm-C integrator. (b) CMFB circuit.

| Parameter           | Value     |

|---------------------|-----------|

| Bias Current        | 5 nA      |

| Input Voltage       | 0.25 V    |

| Common Mode Voltage | Made Zero |

| Drain Voltage       | 0.3 V     |

| Power Consumption   | 15.2 pW   |

# B. Hysteric Comparator

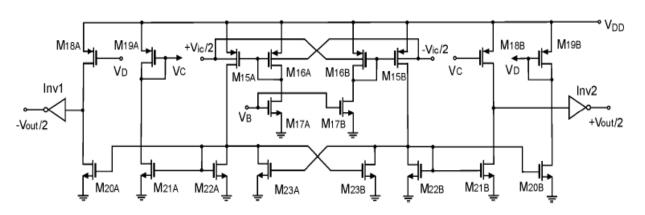

This comparator (Fig. 3) has been implemented using Bulk-Driven (BD) open loop amplifier connected with a negative resistance load (NRL). Input of the differential amplifier (M15 - M17) is supplied from digital to analog converter (DAC) with the support of Vic/2 from DAC circuit.

With the lack of current source at tail, which is a useful feature behaves as an absolute differential amplifier with high common mode rejection ratio (CMRR) and power supply rejection ratio (PSRR). With the addition of transconductance boosting circuitry ( $M_{16\,A, B}$ ), DC voltage will get a gain of 6 dB when compared to common mode BD differential pair.

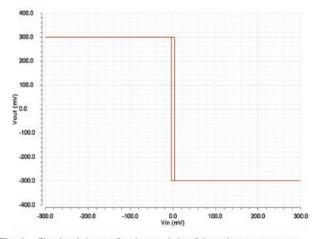

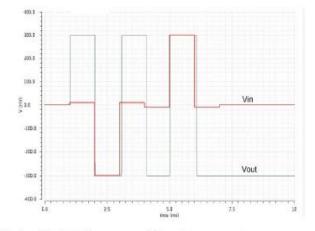

Built-in Hysteresis can be realized using the transistors M22–M23 using NRL circuit. The set of the current mirrors (M18–M22) is used to realize the differential output of the comparator. The additional inverters (Inv1 and Inv2) are used to further improve the quality of the output waveform. Fig. 4 shows the simulated dc transfer characteristic of the comparator, while Fig. 5 shows its transient response for different input voltages. As it can be

noted, the time delay of the comparator () depends on the amplitude of the input signal and varies from 10  $\mu$ s for Vin = 300 mV to 74  $\mu$ s for Vin = 10 mV. Parameters of the comparator are summarized in Table II.

Table.2. Parameters of Comparator

| Parameter         | Value            |

|-------------------|------------------|

| Drain Voltage     | 0.3 V            |

| Input Voltage     | From DAC circuit |

| Power Consumption | 155 nW           |

Fig. 3. BD hysteretic comparator.

Fig. 4. Simulated dc transfer characteristic of the voltage comparator.

Fig. 5. Simulated time response of the voltage comparator.

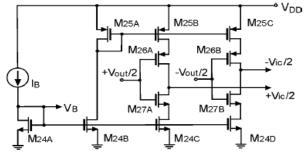

# C. 1 - bit DAC

The DAC circuit implemented in this work was shown in Fig. 6. This circuit was implemented using transistors consisting of four current sources / sinks  $M_{24 C,D}$ ,  $M_{25 B,C}$  and four switches  $M_{26 A,B}$ ,  $M_{27 A,B}$ . The inputs to this circuit are given to switches which are controlled with the outputs of Asynchronous Delta – Sigma Modulator (ADSM).

Based on the output voltage levels, the DAC output current sink or source will be equal to  $I_b$  (5 nA). Therefore, the 1-bit DAC can be considered as a fully differential switched – current source. The mis-matched currents add up with each other thus increases the In<sub>out</sub> offset of ADSM. This DAC circuit is mainly used for converting digital signals to analog signals in the form of bits. But, it converts only one bit per cycle. Therefore, if more the number of bits used in the circuitry; more the number of data will be generated with the

International Journal of Progressive Research in Science and Engineering Volume-1, Issue-8, November-2020

www.ijprse.com

help of very low power and very low voltage which is used highly in future use. The duty cycle of the generated results for Vin = 0 is given as follows.

$$\frac{T_1}{T_1 + T_2} = \frac{1}{2} \left( 1 + \frac{g_m V_{os}}{2I_B} \right)$$

Where,  $V_{os}$  is the inout offset of the ADSM.

The parameters of this 1-bit DAC are given in the below table-IV.

The complete parameters of all the transistors for the benefit of operation regarding the ratio of length and width are tabulated as follows.

Fig. 6. 1-bit DAC circuit.

#### IV. EXPERIMENTAL RESULTS

The overall performances of all the circuitry are comparatively shown as following in the table V.

| Parameter         | [16] 2019 | [7] 2017 | [15] 2017 | This Work |

|-------------------|-----------|----------|-----------|-----------|

| V <sub>DD</sub>   | 0.3 V     | 0.25 V   | 0.4 V     | 0.3 V     |

| Technology        | 180 nm    | 130 nm   | 65 nm     | 54 nm     |

| Туре              | ADSM      | ADSM     | DSM       | ADSM      |

| Power Consumption | 37 nW     | -        | -         | 15.4 pW   |

Above are the comparison of results for different proposed works with some parameters. Present work was implemented in 54 nm CMOS technology with very low voltage and power.

Table.4. Transistor Aspect Ratios and Device Values

| Device                                                                                                            | W/L [µm/µm] |

|-------------------------------------------------------------------------------------------------------------------|-------------|

| M <sub>1</sub> , M <sub>2</sub> , M <sub>3A,B</sub> , M <sub>4A,B</sub> , M <sub>5A,B</sub> - M <sub>8A,B</sub> , | 125/5       |

| M <sub>9A,B</sub> ,M <sub>25A-C</sub>                                                                             | 125/0.5     |

| M <sub>10A,B</sub> , M <sub>11A,B</sub> , M <sub>12A,B</sub> ,                                                    | 50/4        |

| M <sub>13A,B</sub> , M <sub>14</sub> , M <sub>17A,B</sub> , M <sub>24A-D</sub> ,                                  | 60/1.5      |

| M <sub>15A,B</sub> , M <sub>16A,B</sub> , M <sub>18A,B</sub> -M <sub>22A,B</sub>                                  | 25/0.5      |

| M <sub>23A,B</sub>                                                                                                | 30/0.5      |

| $M_{26A,B}M_{27A,B}$                                                                                              | 50/0.5      |

| Device                                                                                                            | value       |

| C <sub>1</sub>                                                                                                    | 50 pF       |

| Inv1, Inv2 (p-MOS)                                                                                                | 10/0.5      |

| Inv1, Inv2 (n-MOS)                                                                                                | 4/0.5       |

#### V. CONCLUSION

In this proposed work, we can achieve very low consumption of power which results in less consumption of area for hardware implementation with the very low voltage supply. Moreover, we can achieve larger size of data in output while increasing the number of bits used in digital to analog converter (DAC); but in this work implemented with only 1bit DAC

#### REFERENCES

- L. H. C. Ferreira and S. R. Sonkusale, "A 60-dB gain OTA operating at 0.25-V power supply in 130-nm digital CMOS process," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 61, no. 6, pp. 1609–1617, Jun. 2014.

- [2]. T. Kulej and F. Khateb, "Design and implementation of sub 0.5-V OTAs in 0.18-µm CMOS," Int. J. Circuit Theory Appl., vol. 46, no. 6, pp. 1129–1143, Jun. 2018.

www.ijprse.com

- [3]. G. D. Colletta, L. H. C. Ferreira, and T. C. Pimenta, "A 0.25-V 22-nS symmetrical bulk-driven OTA for lowfrequency Gm-C applications in 130-nm digital CMOS process," Analog Integr. Circuits Signal Process., vol. 81, no. 2, pp. 377–383, Nov. 2014.

- [4]. T. Kulej and F. Khateb, "Bulk-driven adaptively biased OTA in 0.18 μm CMOS," Electron. Lett., vol. 51, no. 6, pp. 458–460, Mar. 2015.

- [5]. F. Michel and M. S. J. Steyaert, "A 250 mV 7.5  $\mu$ W 61 dB SNDR SC modulator using near-threshold-voltage biased inverter amplifiers in 130 nm CMOS," IEEE J. Solid-State Circuits, vol. 47, no. 3, pp. 709–721, Mar. 2012.

- [6]. L. H. C. Ferreira and S. R. Sonkusale, "A 0.25-V 28-nW 58dB dynamic range asynchronous delta sigma modulator in 130-nm digital CMOS process," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 23, no. 5, pp. 926–934, May 2015.

- [7]. G. D. Colletta, L. H. C. Ferreira, S. R. Sonkusale, and G. V. Rocha, "A 20-nW 0.25-V inverter-based asynchronous delta–sigma modulator in 130-nm digital CMOS process," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 25, no. 12, pp. 3455–3463, Dec. 2017.

- [8]. E. Roza, "Analog-to-digital conversion via duty-cycle modulation," IEEE Trans. Circuits Syst. II, Exp. Briefs, vol. 44, no. 11, pp. 907–914, Nov. 1997.

- [9]. S. Ouzounov, E. Roza, J. A. Hegt, G. van der Weide, and

- [10]. A. H. M. van Roermund, "Analysis and design of high performance asynchronous sigma-delta Modulators with a binary quantizer," IEEE J. Solid-State Circuits, vol. 41, no. 3, pp. 588–596, Mar. 2006.

- [11]. T. Kulej, "0.4-V bulk-driven operational amplifier with improved input stage," Circuits, Syst., Signal Process., vol. 34, no. 4, pp. 1167–1185, Apr. 2015.

- [12]. P. E. Allen and D. R. Holberg, CMOS Analog Circuit Design, 3rd ed. London, U.K.: Oxford Univ. Press, 2012.

- [13]. Y. Yoon, H. Roh, and J. Roh, "A 0.4 V 63 μW 76.1 dB SNDR 20 kHz bandwidth delta-sigma modulator using a hybrid switching integrator," IEEE J. Solid-State Circuits, vol. 50, no. 10, pp. 2342–2352, Oct. 2015.

- [14].J.-E. Park, Y.-H. Hwang, and D.-K. Jeong, "A 0.4-to-1 V Voltage Scalable \_ ADC with Two-Step Hybrid Integrator for IoT Sensor Applications in 65-nm LP CMOS," IEEE Trans. Circuits Syst. II, Exp. Briefs, vol. 64, no. 12, pp. 1417–1421, Dec. 2017.